## Departamento de Ingeniería Telemática y Electrónica

Escuela Técnica Superior de Ingeniería y Sistemas de Telecomunicación

# Contribuciones metodológicas para el desarrollo de aplicaciones de radio software en arquitecturas multiprocesador heterogéneas

## Tesis Doctoral

Autor: Pedro José Lobo Perea

Ingeniero de Telecomunicación por la Universidad Politécnica de Madrid

Directores:

César Sanz Álvaro

Doctor Ingeniero de Telecomunicación por la Universidad Politécnica de Madrid

Eduardo Juárez Martínez

Docteur Ès Sciences Techniques por la École Polytechnique Fédéral de Lausanne

Diciembre de 2021

| AUTOR:<br>DIRECTORES:                                        | D. César Sar  | sé Lobo Perea<br>nz Álvaro<br>Juárez Martínez | Z           |                       |                      |

|--------------------------------------------------------------|---------------|-----------------------------------------------|-------------|-----------------------|----------------------|

| El Tribunal noml<br>Mgfco. y Excmo.<br>los doctores:         |               |                                               | Politécnica | de<br>de Madrid, comp | por el<br>puesto por |

| President                                                    | e: D.         |                                               |             |                       |                      |

| Vocal:                                                       | D.            |                                               |             |                       |                      |

| Vocal:                                                       | D.            |                                               |             |                       |                      |

| Vocal:                                                       | D.            |                                               |             |                       |                      |

| Secretario                                                   | : D.          |                                               |             |                       |                      |

| Suplente:                                                    | D.            |                                               |             |                       |                      |

| Suplente:                                                    | D.            |                                               |             |                       |                      |

| realizado el acto<br>Ingeniería y Siste<br>acuerda otorgar l | mas de Teleco | omunicación de                                |             |                       | -                    |

|                                                              |               | Madrid, a                                     | de          | C                     | de                   |

| EL PRESIDENTE                                                |               |                                               | EL S        | SECRETARIO            |                      |

|                                                              |               |                                               |             |                       |                      |

Contribuciones metodológicas para el desarrollo de aplicaciones de radio software en arquitecturas multiprocesador heterogéneas

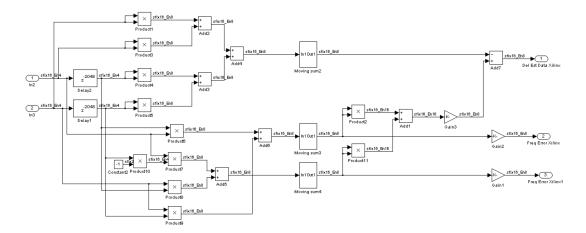

TÍTULO:

LOS VOCALES

Llegar a este punto no hubiera sido posible sin la contribución, la ayuda y el apoyo de muchas personas, a los que quiero expresar desde aquí mi más profundo agradecimiento.

En primer lugar a mis directores de tesis, César y Eduardo, por toda la ayuda que he recibido y por la paciencia infinita que habéis tenido durante todos estos años. Si esto ha llegado a buen término ha sido sin duda gracias a vosotros.

Al resto de compañeros del Grupo de Diseño Electrónico y Microelectrónico (GDEM), tanto presentes (Matías, Ángel, Fernando, Miguel, Jaime, Juan) como pasados (Miguel Ángel, M.C., Rubén), por crear un entorno en el que es un placer trabajar y por estar siempre dispuestos a echar un capote cuando ha hecho falta.

A los estudiantes que han realizado conmigo su proyecto de fin de estudios, y especialmente a Gonzalo, Daniel y Miguel Ángel (Miky), por vuestra contribución a que esto haya sido posible.

A los compañeros del departamento (SEC, primero, y DTE, después), por el apoyo, los momentos de trabajo y los de no trabajo, que afortunadamente empezamos a recuperar poco a poco.

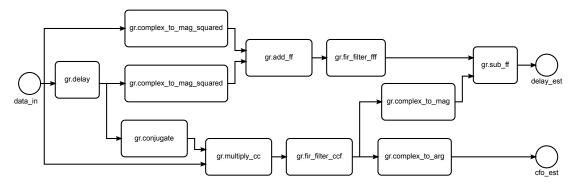

A Gloria, Miguel y Diego, por los muchos ratos que os he robado.

Y a todos aquellos, demasiado numerosos para contarlos, que en algún momento me han dado una palmadita, una colleja o una voz, en función de la situación, el momento y el estilo personal, para animarme a terminar ya de una vez.

Y para finalizar quiero dedicar este momento a la memoria de mis padres. No habéis llegado a verlo, pero sé cuánto lo habríais disfrutado.

# ÍNDICE GENERAL

| Re | sume  | n       |                                                            |     | XIX  |

|----|-------|---------|------------------------------------------------------------|-----|------|

| Ab | strac | t       |                                                            | х   | XIII |

| 1. | Intro |         | ón, objetivos y metodología                                |     | 1    |

|    | 1.1.  | Introd  | lucción                                                    |     | 1    |

|    |       | 1.1.1.  | La radio software                                          |     | 1    |

|    |       | 1.1.2.  | El problema de la arquitectura                             |     | 3    |

|    |       | 1.1.3.  | El problema de la programación                             |     | 6    |

|    |       | 1.1.4.  | GNU Radio: una herramienta de código abierto para radio so | ft- |      |

|    |       |         | ware                                                       |     | 7    |

|    | 1.2.  | Objeti  | vos y metodología                                          |     | 8    |

|    | 1.3.  | Organ   | ización de la memoria                                      |     | 9    |

| 2. | Con   | texto v | estado del arte                                            |     | 11   |

|    | 2.1.  | -       | lucción                                                    |     | 11   |

|    | 2.2.  |         | ándar de televisión digital terrestre DVB-T                |     | 12   |

|    |       | 2.2.1.  | Introducción a la familia de estándares DVB                |     | 12   |

|    |       | 2.2.2.  | Características de DVB–T                                   |     | 14   |

|    |       |         | 2.2.2.1. Adaptación del múltiplex y dispersión de energía  |     | 16   |

|    |       |         | 2.2.2.2. Codificación                                      |     | 16   |

|    |       |         | 2.2.2.1. Codificación externa                              |     | 16   |

|    |       |         | 2.2.2.2. Entrelazado externo                               |     | 17   |

|    |       |         | 2.2.2.3. Codificación interna                              |     | 17   |

|    |       |         | 2.2.2.3. Entrelazado interno                               |     | 18   |

|    |       |         | 2.2.2.4. Mapeado de símbolos                               |     | 18   |

|    |       |         | 2.2.2.4.1. Portadoras de datos                             |     | 19   |

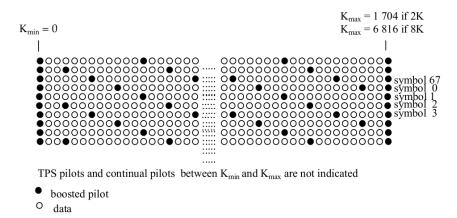

|    |       |         | 2.2.2.4.2. Pilotos continuos y dispersos                   |     | 19   |

|    |       |         | 2.2.2.5. Modulación OFDM                                   |     | 21   |

|    |       |         | 2.2.2.6. Conversión D/A y transmisión                      |     | 21   |

|    | 2.3.  | Radio   | software                                                   |     | 22   |

|    |       | 2.3.1.  | Características de la radio software                       |     | 23   |

|    |       | 2.3.2.  | Aplicaciones de la radio software                          |     | 24   |

|    | 2.4.  | Arquit  | tecturas para radio software                               |     | 25   |

## VIII ÍNDICE GENERAL

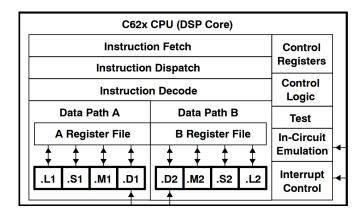

|    |      | 2.4.1.   | Arquitecturas basadas en procesadores de tipo DSP           | 27 |

|----|------|----------|-------------------------------------------------------------|----|

|    |      |          | 2.4.1.1. C6000                                              | 27 |

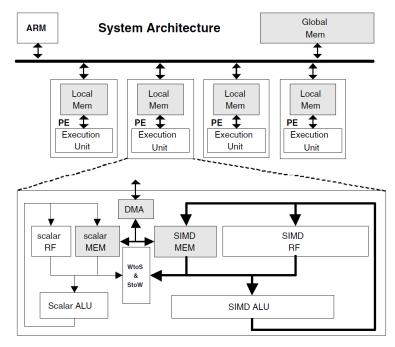

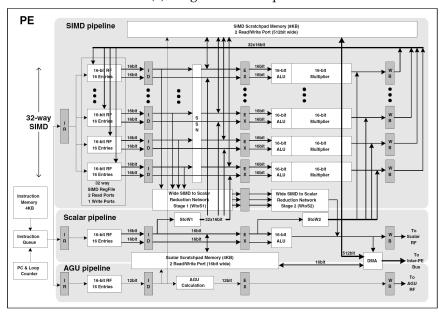

|    |      |          | 2.4.1.2. SODA                                               | 28 |

|    |      |          | 2.4.1.3. LeoCore                                            | 28 |

|    |      |          | 2.4.1.4. Sandblaster                                        | 30 |

|    |      |          | 2.4.1.5. DXP                                                | 31 |

|    |      | 2.4.2.   | Arquitecturas Many-Core                                     | 31 |

|    |      |          | 2.4.2.1. TILEPro64                                          | 32 |

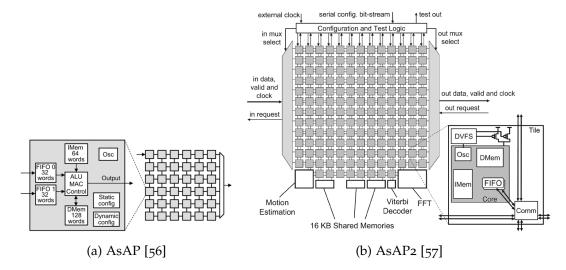

|    |      |          | 2.4.2.2. AsAP y Kilocore                                    | 33 |

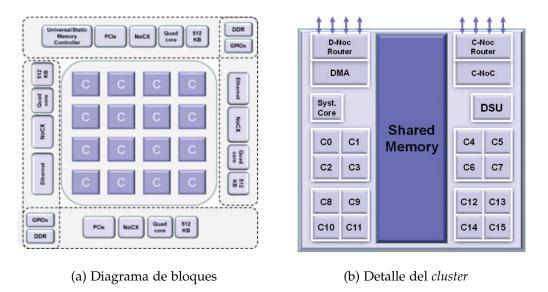

|    |      |          | 2.4.2.3. Kalray MPPA                                        | 34 |

|    |      | 2.4.3.   | Procesadores reconfigurables                                | 35 |

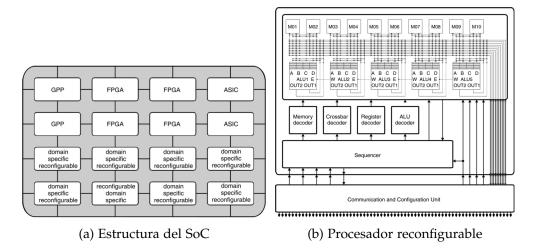

|    |      |          | 2.4.3.1. Montium                                            | 36 |

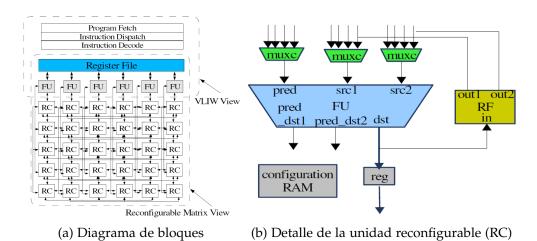

|    |      |          | 2.4.3.2. ADRES                                              | 37 |

|    | 2.5. | Metod    | lología                                                     | 38 |

|    |      | 2.5.1.   | Diseño sin herramientas automáticas                         | 39 |

|    |      | 2.5.2.   | Diseño basado en APIs estándar de paralelización            | 40 |

|    |      |          | 2.5.2.1. OpenMP                                             | 41 |

|    |      |          | 2.5.2.2. OpenCL                                             | 41 |

|    |      |          | 2.5.2.3. Uso de OpenMP y OpenCL en sistemas de radio soft-  |    |

|    |      |          | ware                                                        | 42 |

|    |      | 2.5.3.   | Diseño con herramientas orientadas al dominio de aplicación | 43 |

|    |      |          | 2.5.3.1. Matlab / Simulink                                  | 44 |

|    |      |          | 2.5.3.2. GNU Radio                                          | 46 |

|    | 2.6. | Resun    | nen                                                         | 48 |

| 3. | Dise | eño de a | alto nivel                                                  | 49 |

| _  |      |          | o basado en Matlab / Simulink                               |    |

|    |      |          | Modelo Simulink del receptor                                |    |

|    |      | 3.1.2.   | -                                                           | -  |

|    |      |          | 3.1.2.1. Real-Time Workshop                                 |    |

|    |      |          | 3.1.2.2. HDL Coder                                          | -  |

|    |      |          | 3.1.2.3. System Generator for DSP                           |    |

|    |      | 3.1.3.   | Implementación en la SFF SDR Development Platform           | 59 |

|    |      | 3.1.4.   | Conclusiones                                                | 61 |

|    | 3.2. | Diseño   | o basado en GNU Radio                                       | 61 |

|    |      | 3.2.1.   | Conclusiones                                                | 64 |

|    | 3.3. | -        | nen                                                         | 64 |

| 1  | Port | ado v e  | extensión de GNU Radio                                      | 67 |

| 4.1. Funcionamiento de GNU Radio |          |         |                                                                          |         |

|----------------------------------|----------|---------|--------------------------------------------------------------------------|---------|

|                                  | •        |         |                                                                          | ,<br>71 |

|                                  | 4.2.     |         |                                                                          | ,<br>72 |

|                                  | •        | _       | Consideraciones sobre el uso de GNU Radio en sistemas empo-              | •       |

|                                  |          | •       | _                                                                        | 72      |

|                                  |          | 4.2.2.  |                                                                          | 74      |

|                                  |          | 4.2.3.  |                                                                          |         |

|                                  |          | , ,     | *                                                                        | 76      |

|                                  |          | 4.2.4.  | · · · · · · · · · · · · · · · · · · ·                                    | ,<br>79 |

|                                  |          |         | ,                                                                        | ,<br>80 |

|                                  |          |         | 4.2.4.2. Envío de trabajos y espera de resultados: la API del            |         |

|                                  |          |         | gestor de trabajos                                                       | 82      |

|                                  |          |         | 4.2.4.3. Recepción de mensajes de los aceleradores                       |         |

|                                  | 4.3.     | Resun   | - · · · · · · · · · · · · · · · · · · ·                                  | 85      |

|                                  | <b>.</b> |         |                                                                          | _       |

| 5.                               |          |         |                                                                          | 87      |

|                                  | 5.1.     | -       | mentación en procesador OMAP 3530                                        | -       |

|                                  |          | •       | Ejemplo de implementación de un bloque                                   | -       |

|                                  |          | -       | Resultados obtenidos                                                     |         |

|                                  | 5.2.     | -       | mentación en procesador Keystone II                                      |         |

|                                  |          | 5.2.1.  | ,                                                                        | -       |

|                                  |          |         | 5.2.1.1. API para la gestión de <i>buffers</i> de memoria compartida . 1 | 07      |

|                                  |          |         | 5.2.1.2. Selección de un trabajador concreto para el procesa-            | _       |

|                                  |          |         | miento de un trabajo                                                     |         |

|                                  |          |         | 5.2.1.3. Adaptación del bucle de atención a mensajes 1                   |         |

|                                  |          | 5.2.2.  | Portado y paralelización del receptor DVB–T                              |         |

|                                  |          |         | 5.2.2.1. Portado del decodificador Viterbi a un núcleo C66 1             |         |

|                                  |          |         | 5.2.2.2. Paralelización del decodificador Viterbi                        |         |

|                                  |          |         | 5.2.2.3. FFT                                                             | -       |

|                                  |          | 5.2.3.  |                                                                          |         |

|                                  | 5.3.     | Resun   | nen                                                                      | 28      |

| 6.                               | Sínte    | esis de | la metodología propuesta 1                                               | 29      |

|                                  |          |         | ción de la metodología propuesta a una nueva plataforma 1                | -       |

|                                  |          | 6.1.1.  | Portado de GNU Radio a la plataforma de destino                          | -       |

|                                  |          | 6.1.2.  | Selección de los mecanismos de comunicación entre procesadores1          |         |

|                                  |          | 6.1.3.  |                                                                          |         |

|                                  |          | 6.1.4.  |                                                                          | _       |

|                                  |          | •       | m 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                  | ر<br>32 |

## X ÍNDICE GENERAL

|     | 6.2.   | Resun   | nen                                                           | . 133 |

|-----|--------|---------|---------------------------------------------------------------|-------|

| 7.  | Rest   | ıltados | , aportaciones y trabajo futuro                               | 135   |

|     | 7.1.   | Result  | tados                                                         | . 135 |

|     | •      |         | Metodología de desarrollo para plataformas basadas en siste-  |       |

|     |        | •       | mas multiprocesador heterogéneos                              | . 135 |

|     |        | 7.1.2.  | Extensión de GNU Radio para sistemas multiprocesador hete-    | 55    |

|     |        | ,       | rogéneos                                                      | . 135 |

|     | 7.2.   | Aport   | aciones                                                       |       |

|     | ,      | -       | Publicaciones                                                 | -     |

|     |        | ,       | 7.2.1.1. Publicaciones en revistas indexadas en JCR           |       |

|     |        |         | 7.2.1.2. Publicaciones en congresos internacionales con revi- | 9     |

|     |        |         | sión por pares                                                | . 136 |

|     |        | 7.2.2.  | Dirección de trabajos fin de estudios                         |       |

|     | 7.3.   | -       | o futuro                                                      | -     |

|     | 1      |         |                                                               | 31    |

| Bil | bliog  | rafía   |                                                               | 139   |

| Lis | sta de | acróni  | imos                                                          | 153   |

# ÍNDICE DE FIGURAS

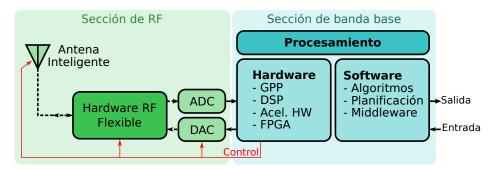

| 1.         | Diagrama genérico de un sistema de radio software 1               |

|------------|-------------------------------------------------------------------|

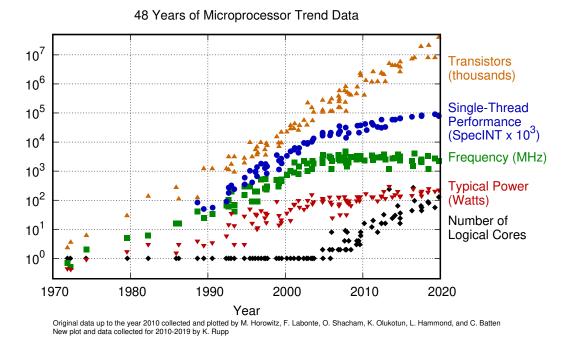

| 2.         | Evolución de los microprocesadores en las últimas cinco déca-     |

|            | das [8]                                                           |

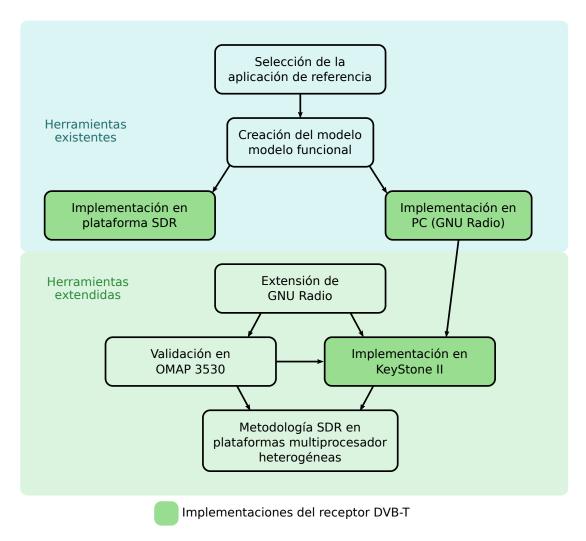

| 3.         | Metodología empleada en el trabajo de tesis                       |

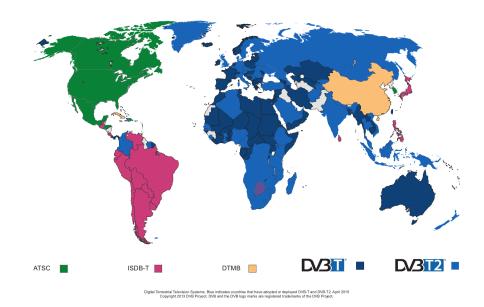

| 4.         | Mapa de adopción de estándares de televisión digital terres-      |

|            | tre [26]                                                          |

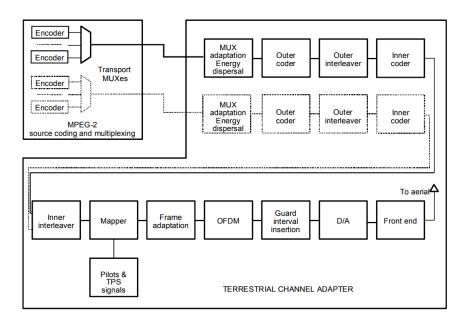

| 5.         | Diagrama de bloques funcional de un transmisor DVB-T [28] . 15    |

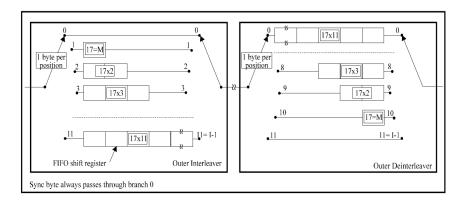

| 6.         | Entrelazado y desentrelazado externo en un transmisor DVB-        |

|            | T [28]                                                            |

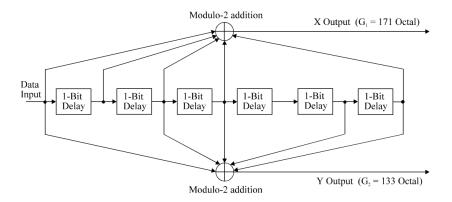

| <b>7</b> ⋅ | Codificador convolucional de DVB-T [28]                           |

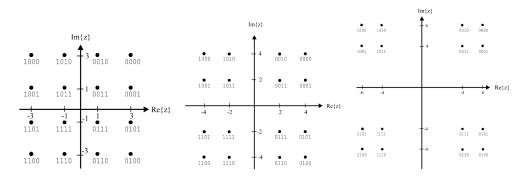

| 8.         | Constelaciones 16QAM en DVB–T con transmisión jerárquica          |

|            | para $\alpha = 1$ , $\alpha = 2$ y $\alpha = 4$ [28]              |

| 9.         | Distribución de los pilotos dispersos en los símbolos OFDM        |

|            | en DVB–T [28]                                                     |

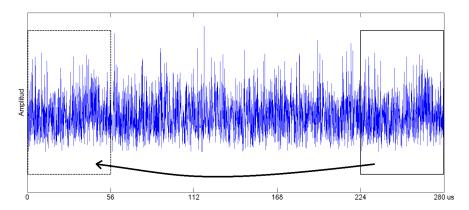

| 10.        | Ejemplo de símbolo OFDM DVB-T con una duración útil de            |

|            | 224 $\mu$ s y longitud del prefijo cíclico 1/4 21                 |

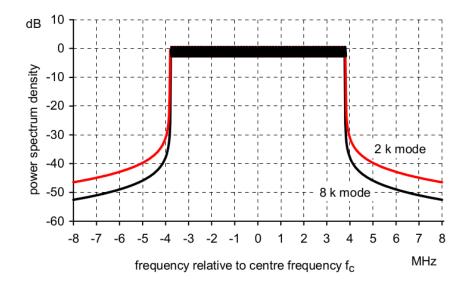

| 11.        | Densidad espectral de potencia de la señal DVB-T para un          |

|            | canal de 8 MHz [28]                                               |

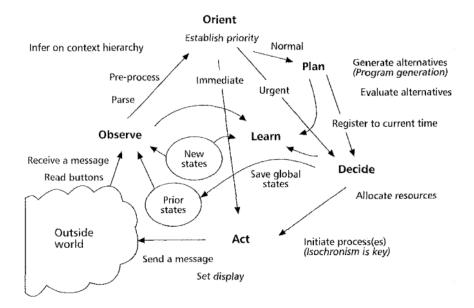

| 12.        | Ciclo cognitivo tal como se describe en [40] 26                   |

| 13.        | Diagrama de bloques de la arquitectura C62x [44] 27               |

| 14.        | Procesador SODA [46]                                              |

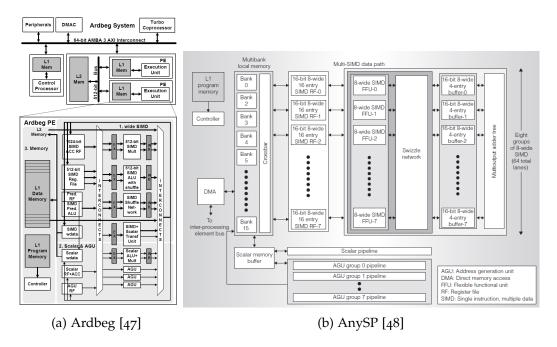

| 15.        | Estructura de los procesadores Ardbeg y AnySP 30                  |

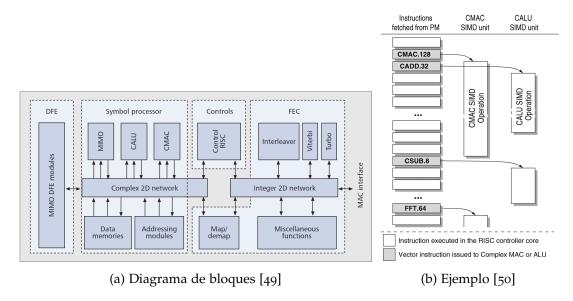

| 16.        | Procesador LeoCore y ejemplo de ejecución de instrucciones        |

|            | en paralelo                                                       |

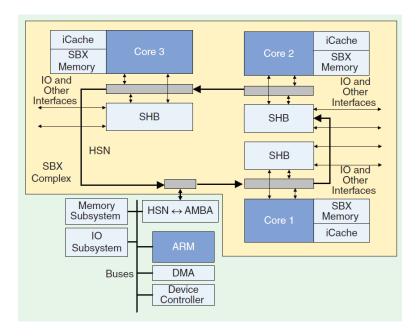

| 17.        | Esquema del SoC SB3500 [42]                                       |

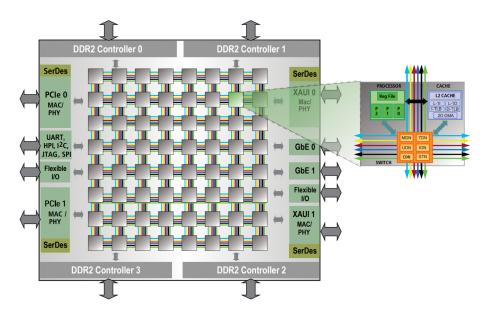

| 18.        | Esquema del procesador TILEPro64 [55]                             |

| 19.        | Estructura de los procesadores AsAP y AsAP2                       |

| 20.        | Arquitectura del procesador MPPA-256 [61]                         |

| 21.        | Arquitectura del procesador Montium [63]                          |

| 22.        | Estructura del procesador ADRES [68]                              |

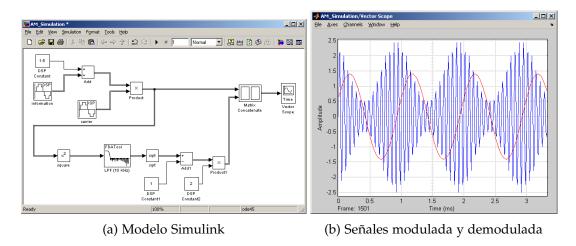

| 23.        | Modelo de modulador y demodulador AM realizado con Si-            |

|            | mulink [78]                                                       |

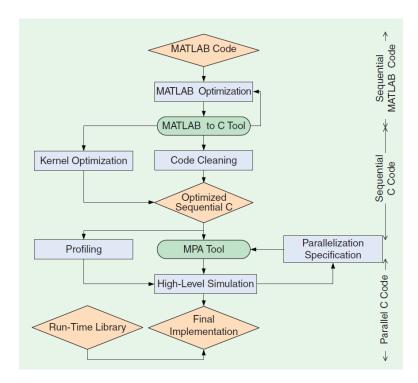

| 24.        | Flujo de diseño para BEAR, una plataforma basada en ADRES [42] 46 |

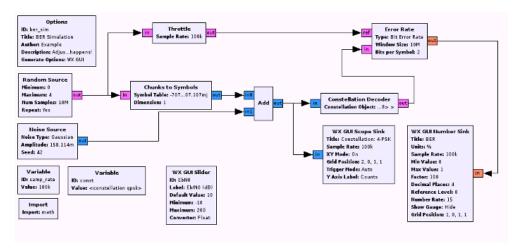

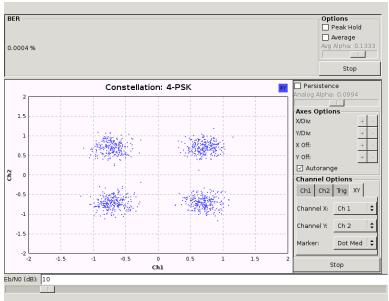

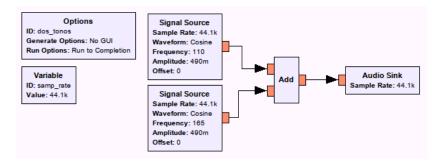

| 25.        | Modelo simulable realizado con GRC [82] 47                        |

## XII ÍNDICE DE FIGURAS

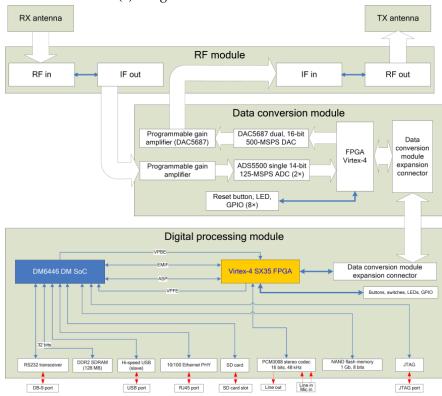

| 26. | Sistema de desarrollo para radio software SFF SDR Development  Platform         |

|-----|---------------------------------------------------------------------------------|

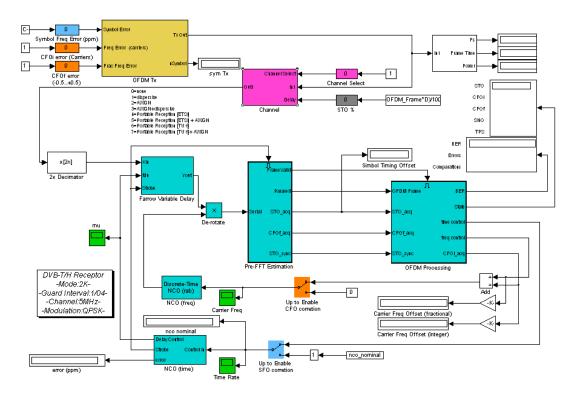

| 27. | Modelo en Simulink del receptor DVB-T 52                                        |

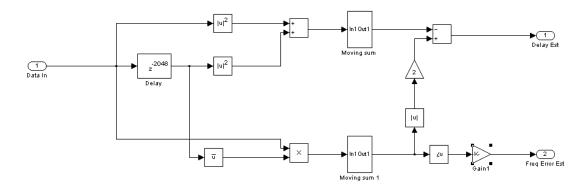

| 28. | Modelo Simulink del estimador del comienzo de símbolo y del                     |

|     | CFOf según el algoritmo descrito en [88] 54                                     |

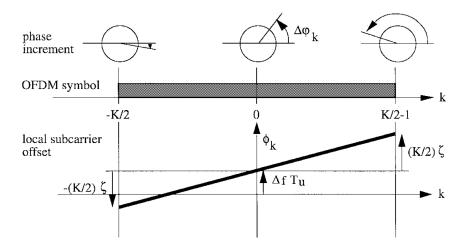

| 29. | Efecto del CFO ( $\Delta f$ ) y el SFO ( $\zeta$ ) en la fase de las portadoras |

|     | individuales del símbolo OFDM recibido [89] 55                                  |

| 30. | Estimador del comienzo de símbolo y del CFOf modificado                         |

|     | para la síntesis con HDL Coder [90] 57                                          |

| 31. | Extracto del informe de síntesis de ISE [90] 58                                 |

| 32. | Estimador del comienzo de símbolo y del CFOf modificado                         |

|     | para la síntesis con System Generator for DSP [92] 59                           |

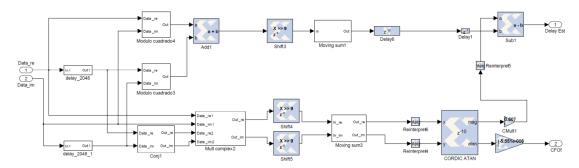

| 33. | Diagrama de bloques del receptor DVB-T [92] 60                                  |

| 34. | Diagrama de bloques del estimador del comienzo de símbolo                       |

|     | y del CFOf implementado en GNU Radio [97] 63                                    |

| 35. | Ejemplo de aplicación GNU Radio realizada con GNU Radio                         |

|     | Companion: suma de dos señales sinusoidales                                     |

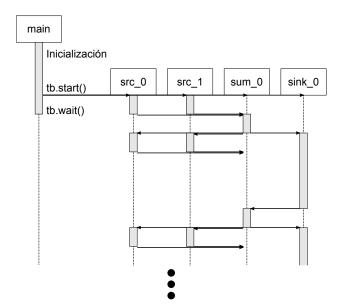

| 36. | Diagrama de ejecución de la aplicación presentada en la figura 35 71            |

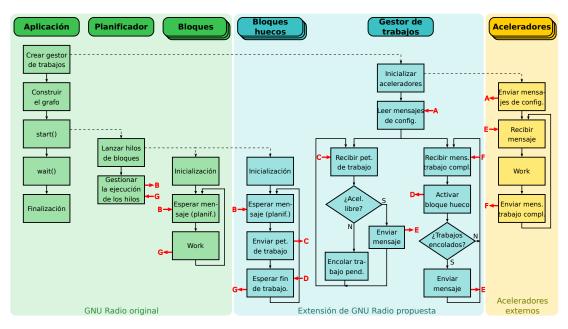

| 37. | Diagrama de flujo del mecanismo propuesto para el uso de                        |

|     | aceleradores en GNU Radio                                                       |

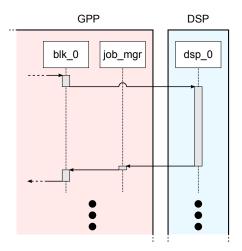

| 38. | Diagrama de hilos de ejecución del mecanismo propuesto para                     |

|     | el uso de aceleradores en GNU Radio                                             |

| 39. | Ejemplo de mapa de recursos del gestor de trabajos 82                           |

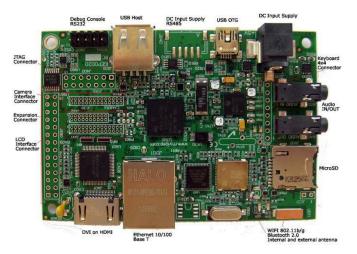

| 40. | Tarjeta IGEP v2 [110]                                                           |

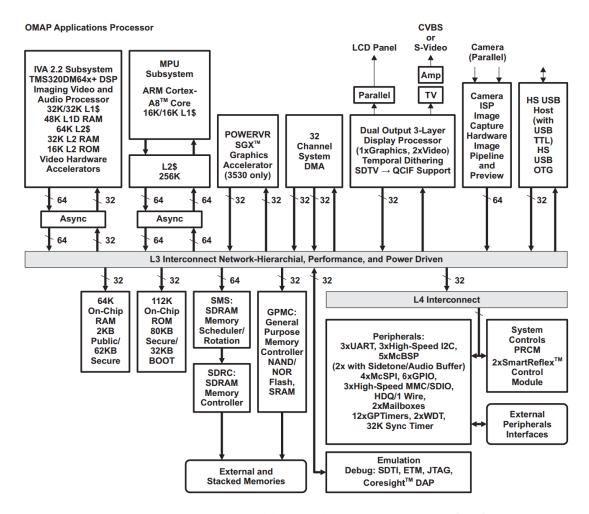

| 41. | Diagrama de bloques del SoC OMAP 3530 [111] 89                                  |

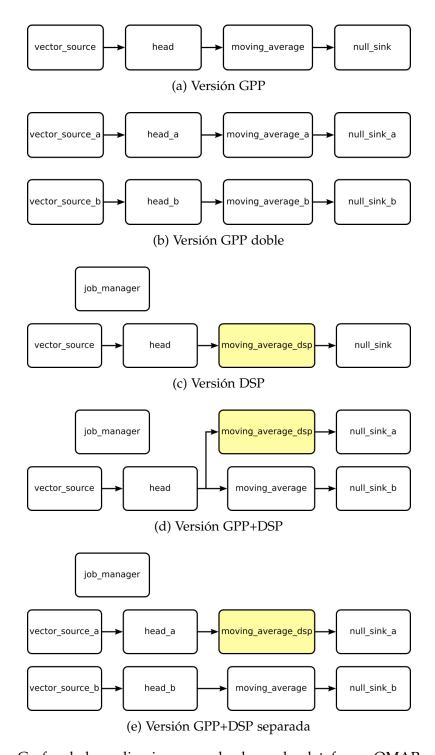

| 42. | Grafos de las aplicaciones empleadas en la plataforma OMAP                      |

|     | 3530 [114]                                                                      |

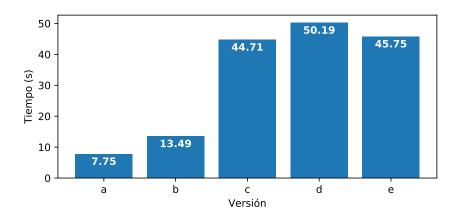

| 43. | Tiempo de ejecución en OMAP 3530 de los grafos mostrados                        |

|     | en la figura 42                                                                 |

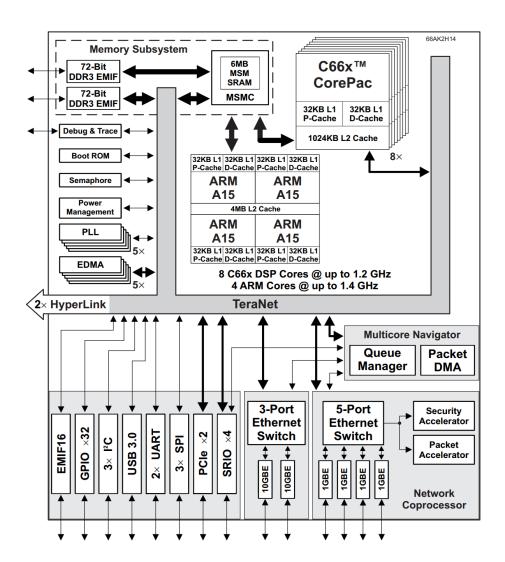

| 44. | Diagrama de bloques del SoC 66AK2H14 [117] 101                                  |

| 45. | Tarjeta de desarrollo EVMK2H                                                    |

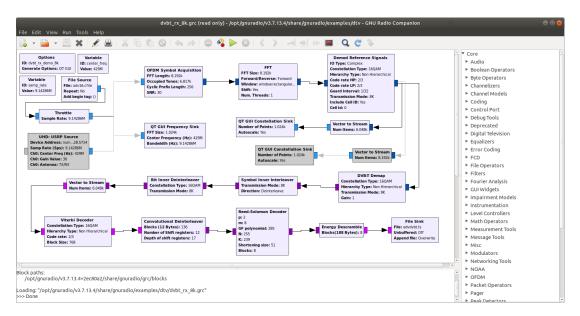

| 46. | Receptor DVB-T distribuido con GNU Radio                                        |

| 47. | Tiempos de ejecución del receptor DVB-T ejecutando el deco-                     |

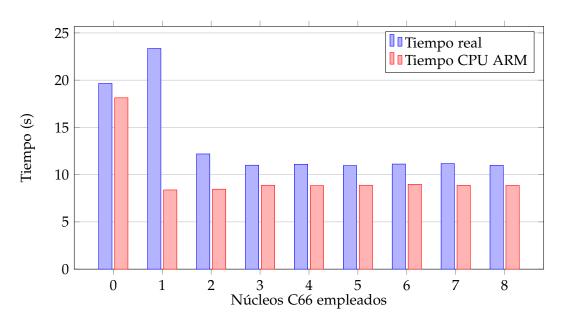

|     | dificador Viterbi en un núcleo C66                                              |

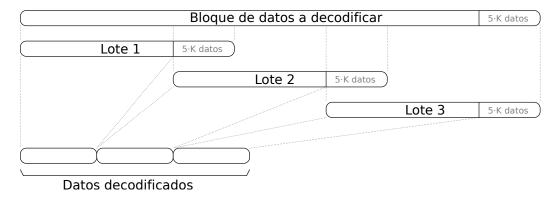

| 48. | Paralelización del algoritmo de Viterbi según [129]119                          |

| 49. | Tiempos de ejecución del receptor DVB-T ejecutando el deco-                     |

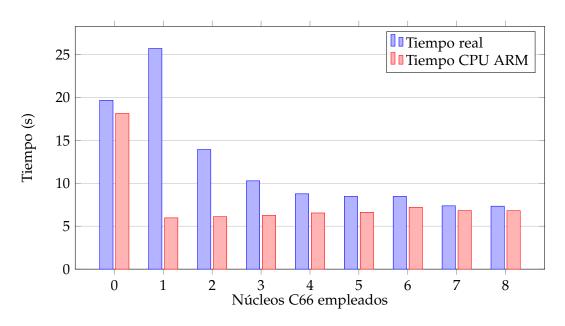

|     | dificador Viterbi en varios núcleos C66                                         |

## ÍNDICE DE FIGURAS XIII

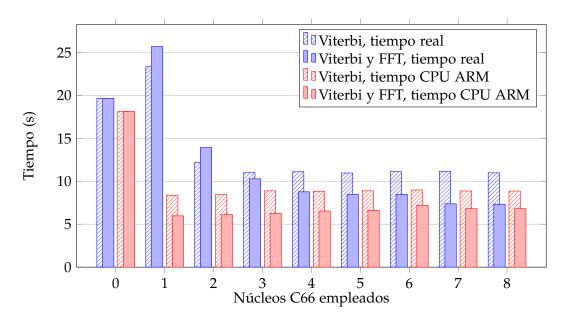

| 50. | Tiempos de ejecución del receptor DVB-T ejecutando el deco- |

|-----|-------------------------------------------------------------|

|     | dificador Viterbi y la FFT en varios núcleos C66            |

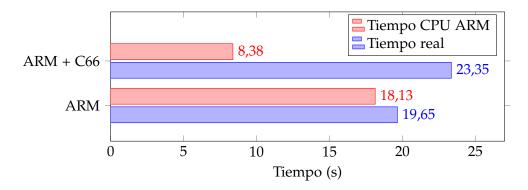

| 51. | Comparación de los tiempos de ejecución del receptor DVB-T  |

|     | con el cálculo de la FFT en los núcleos ARM o C66 127       |

# ÍNDICE DE TABLAS

| 1. | Comparación entre ciclos de reloj consumidos por el código         |

|----|--------------------------------------------------------------------|

|    | generado por Real-Time Workshop y el codificado manual-            |

|    | mente [90]                                                         |

| 2. | Rendimiento obtenido por el receptor implementado con GNU          |

|    | Radio [97]                                                         |

| 3. | Características de la señal DVB-T empleada en todas las pruebas111 |

| 4. | Resultados del perfilado del receptor DVB-T                        |

# ÍNDICE DE LISTADOS

| 1. | Código Python correspondiente al diagrama de bloques de la figura 34 | 62  |

|----|----------------------------------------------------------------------|-----|

| 2. | Código Python generado a partir del grafo de la figura 35            |     |

| 3. | Ejemplo de código C++ para un bloque que suma dos señales            | -   |

| 4. | API pública del gestor de trabajos                                   | 82  |

| 5. | Definición simplificada del descriptor de trabajo                    | 92  |

| 6. | Definición, constructor y destructor del bloque gdsp_moving_avg_s    | 94  |

| 7. | Método work del bloque gdsp_moving_avg_s                             | 96  |

| 8. | Código DSP para el bloque gdsp_moving_avg_s                          | 97  |

| 9. | Definición de la tabla de funciones                                  | 109 |

| 10 | . Bucle de atención a mensajes                                       | 109 |

| 11 | . Constructor del bloque viterbi_decoder_bb                          | 114 |

| 12 | . Método work del bloque viterbi_decoder_bb                          | 115 |

| 13 | . Método work del bloque viterbi_decoder_sl_bb                       | 119 |

| 14 | . Método work del bloque fft_vcc                                     | 123 |

| 15 | . Código C66 para el bloque fft_vcc                                  | 125 |

|    |                                                                      |     |

La radio software (Software Radio) o radio definida por software (Software Defined Radio, SDR) consiste en la implementación de sistemas de radiocomunicación empleando procesadores programables en lugar de hardware específico. El primer uso del término data de hace casi cuatro décadas, pero fue en la segunda mitad de la década de los 90 cuando el concepto tomó impulso gracias a que la tecnología disponible en ese momento comenzó a hacer ya posible su uso práctico, y en la actualidad puede afirmarse que todos los dispositivos de radiocomunicaciones emplean esta técnica en mayor o menor medida.

A pesar de sus evidentes ventajas en cuanto a flexibilidad y rapidez de desarrollo frente a los sistemas basados en *hardware* específico, el principal problema de la radio *software* ha estado siempre en sus elevados requerimientos en cuanto a capacidad de cómputo. Aunque el avance continuo de la tecnología permite construir sistemas cada vez más capaces, las prestaciones que se demandan del equipamiento de comunicaciones crecen de manera simultánea, de modo que los sistemas de radio *software* siempre requieren la máxima capacidad de cómputo que la tecnología sea capaz de ofrecer. Esto pasa, desde hace ya casi dos décadas, por el uso de sistemas multiprocesador, debido a la dificultad de mantener el ritmo de mejora en el rendimiento de un único procesador a base de avances en la tecnología de fabricación. A menudo, además, estos sistemas multiprocesador son heterogéneos; es decir, emplean procesadores de varios tipos, con distintas características y capacidades.

El uso de sistemas multiprocesador heterogéneos plantea un nuevo reto: a pesar de que los primeros sistemas con multiprogramación datan de los años 60, el problema de cómo programar de forma eficiente este tipo de sistemas dista mucho de estar resuelto de forma general. Esto es además especialmente evidente en determinados nichos de aplicación, y en el ámbito concreto de la radio *software* las técnicas de programación que han recibido mayor atención y recursos de investigación a nivel general en estas dos últimas décadas no proporcionan resultados satisfactorios o lo hacen a costa de requerir un esfuerzo considerable.

Este es el contexto en el que se desarrolla esta tesis doctoral, cuyo objetivo es desarrollar una metodología de programación para aplicaciones de radio *software* sobre sistemas multiprocesador heterogéneos. Para conseguir este objetivo se han seguido una serie de pasos que se resumen a continuación.

En primer lugar se ha seleccionado una aplicación de referencia lo suficientemente compleja para permitir evaluar los resultados obtenidos. La aplicación seleccionada ha sido un receptor de televisión digital terrestre DVB–T.

A continuación se ha empleado Matlab/Simulink, una herramienta comercial que es prácticamente un estándar *de facto* en el ámbito del procesado de señal, para crear un modelo funcional del receptor DVB–T, y se ha usado después este modelo para implementar el receptor en una plataforma *hardware* específica para radio *software* que combina un DSP y una FPGA. Este proceso ha servido para evaluar las posibilidades que ofrecen varias herramientas de diseño de alto nivel basadas en Simulink.

En paralelo con este trabajo se ha realizado una búsqueda de herramientas que sirvieran como base para atacar el problema que se pretendía resolver en este trabajo de tesis, la programación de aplicaciones de radio *software* en sistemas multiprocesador heterogéneos. Se ha decidido basar el trabajo en GNU Radio, un kit de *software* libre para desarrollo para aplicaciones de radio *software* distribuído con licencia GNU GPL. Aunque en principio es una herramienta pensada para desarrolo en PC, sus características hacen posible adaptarla a plataformas empotradas especializadas, y al distribuirse con licencia GPL la disponibilidad del código fuente para su estudio y modificación es total. El trabajo de modelado realizado con Matlab/Simulink ha servido de base para realizar una segunda implementación del receptor DVB–T basada en GNU Radio.

Tal como se distribuye, GNU Radio puede emplear varios procesadores pero únicamente en sistemas SMP (multiproceso simétrico); por tanto, el siguiente paso ha sido diseñar una extensión de GNU Radio que posibilita su uso en plataformas específicas para radio *software* sacando partido de todos los recursos (procesadores o aceleradores especializados) que puedan ofrecer. Esta extensión se ha diseñado de modo que sea lo más general posible y pueda adaptarse a cualquier plataforma para la que existan unas herramientas mínimas: un compilador de C++ y un mecanismo de comunicación entre procesadores accesible mediante una API POSIX estándar. La metodología propuesta es aplicable en plataformas que tengan aceleradores especializados en funciones específicas o aceleradores programables que puedan implementar una o varias funciones, sin limitaciones a priori en cuanto al número o tipo de aceleradores.

La extensión a GNU Radio se ha implementado en dos plataformas *hardware* distintas. En primer lugar se ha utilizado una plataforma relativamente sencilla basada en un procesador OMAP 3530 de Texas Instruments, que combina un procesador de propósito general y un DSP. Esta primera implementación ha servido como prueba de concepto para validar el diseño de la extensión.

En segundo lugar se ha empleado una plataforma mucho más potente basada en un procesador de la familia KeyStone II del mismo fabricante, que cuenta con cuatro procesadores de propósito general y ocho DSPs. Tras adaptar la extensión de GNU Radio a esta nueva plataforma se ha portado a la misma el receptor DVB–T, trasladando después dos de las tareas con mayor carga computacional (la decodificación convolucional con el algoritmo de Viterbi y el cálculo de la FFT) a los DSPs. Se ha conseguido de este modo una reducción de un 63 % en el tiempo de ejecución del receptor respecto a la versión que emplea únicamente los procesadores de propósito general. Estos resultados confirman que la versión extendida de GNU Radio es capaz de distribuir las tareas de manera eficiente entre los recursos disponibles en la plataforma objetivo.

Finalmente se ha sintetizado todo el trabajo realizado en una propuesta de metodología para el desarrollo de aplicaciones de radio *software* en arquitecturas multiprocesador heterogéneas basada en la extensión de GNU Radio, y se ha creado una implementación de referencia que puede emplearse como base para su uso en nuevas plataformas *hardware*. Esta implementación de referencia está disponible en el servidor Gitlab del Centro de Investigación en Tecnologías Software y Sistemas Multimedia para la Sostenibilidad (CITSEM) de la Universidad Politécnica de Madrid.

Software Radio or Software Defined Radio (SDR) is the implementation of radio communication systems using programmable processors instead of dedicated hardware. The first use of the term dates back almost four decades, but it was in the second half of the 1990s that the concept gained momentum as the technology available at that time began to make its practical use possible, and today it can be said that all radio devices employ this technique to a greater or lesser extent.

Despite its obvious advantages in terms of flexibility and speed of development over systems based on dedicated hardware, the main problem with software radio has always been its high computational requirements. Although the continuous advance of technology makes it possible to build ever more capable systems, the performance demanded from communications equipment is also constantly growing, so that radio software systems always require the maximum computational capacity that the technology is able to offer. Since almost two decades now, this has led to the use of multiprocessor systems, due to the difficulty of keeping pace with improvements in the performance of a single processor based on advances in manufacturing technology. In addition, these multiprocessor systems are often heterogeneous, i.e. they use processors of various types, with different characteristics and capabilities.

The use of heterogeneous multiprocessor systems poses a new challenge: although the first systems with multiprogramming date back to the 1960s, the problem of how to efficiently program such systems is far from being generally solved. This is particularly true in certain application niches; for the specific field of radio software, the programming techniques that have received the most attention and research resources at a general level in the last two decades do not provide satisfactory results or do so at the cost of considerable effort.

This is the context in which this Ph.D. thesis is developed, whose objective is to develop a programming methodology for radio software applications on heterogeneous multiprocessor systems. The steps that have been followed in order to achieve this objective are summarised below.

First, a sufficiently complex reference application has been selected to allow the evaluation of the results obtained. The selected application has been a DVB-T digital terrestrial television receiver.

Matlab/Simulink, a commercial tool that is practically a de facto standard in the field of signal processing, has been used to create a functional model of the DVB-T receiver. This model has been used to implement the receiver on a radio-specific

hardware platform combining a DSP and an FPGA. This process has been used to evaluate the possibilities offered by several high-level design tools based on Simulink.

At the same time, a search has been carried out for tools that could be used as a basis to attack the problem that this thesis work was intended to solve, the programming of radio software applications in heterogeneous multiprocessor systems. The choice was GNU Radio, a free software development kit for radio software applications distributed under the GNU GPL licence. Although it is a tool designed for PC development, its characteristics make it possible to adapt it to specialised embedded platforms, and as it is distributed under the GPL licence, the source code is fully available for study and modification. The modelling work carried out with Matlab/Simulink has served as the basis for a second implementation of the DVB–T receiver based on GNU Radio.

As distributed, GNU Radio can use multiple processors but only on SMP (symmetric multiprocessing) systems; therefore, the next step has been to design an extension to GNU Radio that makes it possible to use it on specific software radio platforms, taking advantage of all the resources (processors or specialised accelerators) that they can offer. This extension has been designed to be as general as possible and can be adapted to any platform for which minimum tools exist: a C++ compiler and an interprocessor communication mechanism accessible through a standard POSIX API. The proposed methodology is applicable to platforms that have accelerators specialised in specific functions or programmable accelerators that can implement one or several functions, without a priori limitations on the number or type of accelerators.

The extension to GNU Radio has been implemented on two different hardware platforms. First, a relatively simple platform based on a Texas Instruments OMAP 3530 processor, which combines a general purpose processor and a DSP, has been used. This first implementation has served as a proof of concept to validate the extension design.

Secondly, a much more powerful platform based on a processor of the KeyStone II family from the same manufacturer, which has four general-purpose processors and eight DSPs, has been used. After adapting the GNU Radio extension to this new platform, the DVB-T receiver has been ported to it, and two of the most computationally intensive tasks (the convolutional decoding with the Viterbi algorithm and the FFT calculation) have been transferred to the DSPs. This has resulted in a 63 % reduction in receiver execution time compared to the version using only the general-purpose processors. These results confirm that the extended version of GNU Radio is able to distribute the tasks efficiently among the resources available on the target platform.

Finally, all the work has been synthesised into a proposed methodology for the development of radio applications on heterogeneous multiprocessor architectures based

on the GNU Radio extension, and a reference implementation has been created that can serve as a basis for use on new hardware platforms. This reference implementation is available on the Gitlab server of the Centro de Investigación en Tecnologías Software y Sistemas Multimedia para la Sostenibilidad (CITSEM) of the Universidad Politécnica de Madrid.

En este capítulo se introduce la temática y la motivación de la tesis doctoral, se definen los objetivos de la investigación, se explica la metodología seguida durante el trabajo de investigación y se define la estructura del resto de la memoria.

#### 1.1 INTRODUCCIÓN

### 1.1.1 La radio software

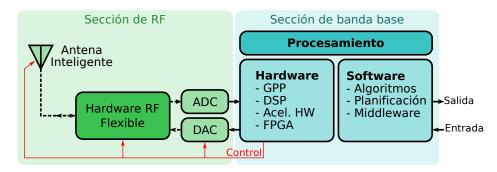

El concepto de radio *software* (*Software Radio*) o radio definida por *software* (*Software Defined Radio*, *SDR*) consiste en la implementación de sistemas de radiocomunicación empleando procesadores programables en lugar de *hardware* específico. La figura 1 muestra un diagrama genérico de una radio *software*.

Figura 1: Diagrama genérico de un sistema de radio software

La radio *software* lleva siendo objeto de investigación desde hace más de tres décadas [1]. Las ventajas de esta idea respecto a los sistemas realizados con *hardware* específico parecen claras a priori:

- Un mismo equipo *hardware* puede implementar varios protocolos de comunicaciones inalámbricas¹, a veces incluso de forma simultánea.

- Es posible actualizar el equipamiento en servicio ya existente para implementar nuevos protocolos de comunicaciones inalámbricas.

<sup>1</sup> En ciertos ámbitos cada procotolo inalámbrico recibe el nombre de forma de onda.

Una implementación basada en software suele resultar más rápida y económica que una basada en hardware específico, lo que permite reducir tanto ciclos de desarrollo como costes.

A pesar de estas ventajas, la radio *software* tiene un claro inconveniente, que es la enorme capacidad de cómputo que requiere. El demostrador Speakeasy fase I [2], presentado en 1995 y considerado como la primera implementación completa de una radio *software*, necesitaba emplear decenas de procesadores de señal TMS320C40, la punta de la tecnología en aquel momento, y ocupaba un armario de dos metros de altura, todo ello para implementar sistemas que proporcionaban un canal de voz y datos con tasas binarias de algunas decenas de kbps.

Los progresos en la tecnología de fabricación de circuitos electrónicos y en las arquitecturas *hardware* para procesado de señal han aumentado enormemente la capacidad de cómputo disponible desde entonces, pero también lo han hecho las prestaciones demandadas de los sistemas de radiocomunicaciones. Por citar únicamente algunos ejemplos relevantes:

- La telefonía móvil ha pasado de ofrecer tasas binarias en el orden de los 400 kbps usando canales de 200 kHz con una única portadora en los sistemas 2G a mediados de la década de los 90, a tasas del orden de 1 Gbps empleando canales de hasta 100 MHz con 4096 portadoras² en los sistemas 5G que se están desplegando actualmente.

- El estándar IEEE 802.11g, publicado en 2003 y conocido actualmente como Wi-Fi 3, permitía obtener una tasa binaria máxima de 54 Mbps empleando 64 portadoras en canales de hasta 20 MHz. El estándar IEEE 802.11ax (WiFi 6), publicado recientemente, permite alcanzar los 10 Gbps empleando 512 portadoras individuales en un ancho de banda de 160 MHz.

- El estándar de televisión digital DVB–T, publicado en 1997, permite transmitir hasta 32 Mbps en un canal de 8 MHz empleando hasta 8192 portadoras. Su sucesor DVB–T2, publicado en 2008, soporta una tasa binaria máxima de unos 50 Mbps en el mismo canal, aumentando el número máximo de portadoras hasta 32768.

<sup>2</sup> Todos los sistemas modernos emplean alguna variación de OFDM. En este y los siguientes ejemplos, el número de portadoras indicado corresponde al tamaño de la FFT que es necesario emplear. El número de portadoras útiles suele ser del orden del 75 u 80 % del tamaño de la FFT.

■ Las modulaciones empleadas en las portadoras individuales han evolucionado desde 4 o 6 bits por símbolo (16QAM, 64QAM) en los sistemas de principios de siglo a 10 bits por símbolo (1024QAM) en los sistemas actuales³.

Los algoritmos de corrección de errores empleados en los sistemas mencionados han ido incrementando en general sus requisitos computacionales de forma proporcional a las tasas binarias empleadas, aunque la investigación en este campo ha permitido encontrar algoritmos más eficientes (LDPC, códigos polares combinados con CRC) que los empleados en los sistemas más antiguos mencionados (códigos convolucionales y Turbo) [3, 4].

En resumen, el avance tecnológico ha hecho viable construir sistemas de radio *software* prácticos, pero estos demandan siempre la máxima capacidad computacional que la tecnología pueda proporcionar en cada momento. El lector interesado puede encontrar una extensa introducción a la radio *software* y su estado actual en [5].

## 1.1.2 El problema de la arquitectura

El avance tecnológico al que se ha hecho referencia llegó a un punto de inflexión a mediados de la década de los 2000. Hasta ese momento el incremento en el rendimiento de los procesadores estaba sustentado en gran medida en la conocida ley de Moore [6, 7], que lleva cumpliéndose desde hace más de cincuenta años: el número de componentes (transistores) que pueden introducirse en un circuito integrado se duplica cada dos años aproximadamente. La reducción en tamaño de los transistores implicaba un aumento en la velocidad de funcionamiento, y de ahí buena parte del aumento del rendimiento.

Pero el aumento de la densidad de integración de los transistores y de su frecuencia de funcionamiento implican también un aumento de la potencia disipada por unidad de superficie, y a mediados de los 2000 se llegó a lo que se ha llamado el muro de potencia (power wall): la potencia máxima disipable en un circuito integrado por unidad de superficie, que está en el entorno de los 100  $W/cm^2$ .

El efecto de este muro de potencia puede verse claramente en la figura 2, que muestra la evolución de varias características de procesadores de propósito general en las últimas cinco décadas<sup>4</sup>. Mientras que la densidad de integración ha crecido a ritmo

<sup>3</sup> Todos los sistemas mencionados pueden emplear varios esquemas de modulación para las portadoras individuales; los esquemas indicados son los más complejos (es decir, con mayor número de bits por símbolo) soportados en cada sistema.

<sup>4</sup> Aunque la figura 2 está construida con datos de microprocesadores de propósito general o para sistemas de cálculo científico de alto rendimiento (HPC, *High Performance Computing*), la situación es extrapolable a cualquier otro tipo de sistema basado en procesadores programables.

prácticamente constante durante todo este tiempo (triángulos anaranjados), la frecuencia de funcionamiento (cuadrados verdes) y la potencia consumida (triángulos invertidos marrones) se han estancado desde 2003 aproximadamente. Esta limitación ha reducido notablemente el ritmo de incremento en el rendimiento de un único procesador (círculos azules), que ya solo crece por las mejoras a nivel de arquitectura.

Figura 2: Evolución de los microprocesadores en las últimas cinco décadas [8]

La solución se ha buscado, tal como se muestra en la figura mediante los rombos negros, en los sistemas multiprocesador. Si bien ya no es posible incrementar la frecuencia de funcionamiento, la evolución tecnológica ha hecho posible integrar varios procesadores (que pasan a denominarse núcleos o *cores*) en cada chip, y en la actualidad es muy habitual encontrar en casi cualquier tipo de sistema procesadores con dos, cuatro u ocho núcleos, o incluso varias decenas en sistemas de alto rendimiento.

Otra variante de esta forma de seguir buscando la mejora en el rendimiento que pone especial énfasis en conseguir además la máxima eficiencia energética ha sido el desarrollo de procesadores específicos para una aplicación concreta, conocidos como ASIP (*Application-Specific Instruction-set Processor*). Además del uso de varios núcleos, estos procesadores emplean dos estrategias:

■ Añadir a los núcleos, o a algunos de ellos, unidades funcionales específicas para determinadas operaciones. Estos núcleos pueden emplear un juego de

instrucciones (ISA, *Instruction Set Architecture*) propio o, más frecuentemente, se puede hacer sobre un núcleo cuya ISA sea extensible, añadiendo instrucciones que empleen la unidad funcional específica [9, 10].

Añadir coprocesadores hardware especializados en determinadas tareas que resulten especialmente pesadas para los núcleos programables.

En el ámbito específico de la radio *software* los ASIPs pueden tener instrucciones que realicen operaciones aritméticas sobre números complejos o sobre cuerpos de Galois<sup>5</sup> (GF, *Galois Field*), o que permitan intercalar o mezclar bits o bytes en una palabra. El uso de coprocesadores *hardware* especializados contradice los fundamentos de la radio *software*, pero no es extraño encontrarlos como solución de compromiso para determinadas operaciones<sup>6</sup> en sistemas con requisitos de consumo energético estrictos, ya que el *hardware* dedicado siempre es más eficiente en términos energéticos que el programable.

Por otro lado, de forma más o menos simultánea a la generalización de los procesadores con varios núcleos empezó a explorarse el uso de las unidades de procesado de gráficos (GPU, *Graphics Processing Unit*) para computación de propósito general. Los algoritmos empleados en el procesado de gráficos se basan con mucha frecuencia en la repetición de operaciones relativamente simples en múltiples áreas de una imagen de forma independiente; por ello, la arquitectura de las GPUs ha estado basada desde hace mucho tiempo en un número elevado de procesadores sencillos que aplican en paralelo una determinada transformación a las distintas partes de la imagen. De nuevo, la evolución tecnológica ha permitido que estos procesadores crezcan cada vez más en complejidad y en número, y a principios de la década de los 2000 empezó a explorarse la utilización de GPUs para computación de propósito general (GPGPU, *General-Purpose computing on GPU*) [11, 12]. Poco después este tipo de uso de las GPUs comenzó a recibir pleno soporte por parte de sus fabricantes, y en 2007 NVIDIA publicó la primera versión del API CUDA (acrónimo de *Compute Unified Device Architecture*).

En la actualidad el uso de GPGPU está enormemente extendido y pueden proporcionar un rendimiento (tanto bruto como por vatio) notablemente superior al de los procesadores de propósito general, pero solo si la aplicación es adecuada a sus características. Esto implica fundamentalmente dos cosas: que la carga computacional esté asociada mayoritariamente a un único algoritmo, y que dicho algoritmo posea un alto grado de paralelismo a nivel de datos, es decir, que se pueda aplicar de forma

<sup>5</sup> Los cuerpos de Galois son estructuras algebraicas de utilidad en áreas como la codificación contra errores o la criptografía.

<sup>6</sup> Típicamente el cálculo de la FFT o la decodificación de códigos de protección contra errores.

simultánea e independiente a un número elevado de grupos de datos. Como se verá más adelante, las aplicaciones de radio *software* no suelen cumplir estas características y por tanto no son en general especialmente adecuadas para su implementación mediante GPGPU.

De una u otra manera, desde hace ya años las plataformas que se emplean para la implementación de sistemas de radio *software* están siempre basadas en sistemas multiprocesador, a menudo heterogéneos (es decir, que emplean núcleos procesadores de varios tipos y con diferentes capacidades).

## 1.1.3 El problema de la programación

Como se ha descrito en el apartado anterior, el estancamiento en el aumento de rendimiento debido a factores tecnológicos se palía, al menos en parte, con el incremento en el número de núcleos. Sin embargo esta solución introduce un nuevo problema: la programación de estos sistemas multiprocesador. A pesar de que los primeros sistemas con multiprogramación aparecieron a principios de la década de 1960 [13] y de que este ha sido un campo objeto de intensa investigación desde entonces, el problema de cómo programar sistemas multiprocesador de forma eficiente y razonablemente sencilla dista mucho de estar resuelto de forma general [14], y más aún en el caso de sistemas heterogéneos.

Han existido, y existen aún, decenas de aproximaciones y soluciones a este problema, y la característica común que todas comparten es que ninguna puede atender todas las posibles áreas de aplicación. En [15] se describen algunas propuestas relativamente recientes orientadas al ámbito del procesado de señal e imagen; la mayoría de ellas proporcionan herramientas para aprovechar únicamente el paralelismo a nivel de datos, obviando el paralelismo a nivel de tarea inherente a las aplicaciones de radio software, no dan soporte al uso de procesadores especializados, son difícilmente trasladables a sistemas empotrados, son soluciones propias (productos comerciales) que no pueden emplearse en plataformas no soportadas por el fabricante, o una combinación de varios de estos factores. A la hora de implementar una aplicación de radio software en una plataforma propia es difícil que alguna de las soluciones descritas resulten útiles sin emplear un esfuerzo considerable.

Por otro lado, existe una tendencia significativa hacia el empleo de APIs estandarizadas para la programación de sistemas heterogéneos, especialmente los que emplean GPGPU y hardware programable (FPGAs, Field Programmable Gate Array). El uso de estas APIs es útil para tratar de homogeneizar la programación en distintas plataformas y aplicaciones, lo que siempre ayuda a reducir el esfuerzo requerido y permite rentabilizar las habilidades aprendidas [16].

Las APIs estándar más extendidas son OpenMP [17] y OpenCL [18]. La primera se estandarizó en 1997 y nació originalmente para facilitar la programación de sistemas multiprocesador simétricos, aunque en sucesivas revisiones se le ha añadido soporte para el uso de aceleradores *hardware*. La segunda es bastante posterior (su primera versión data de 2009) y tiene como objetivo ser el Java (*"write once, run everywhere"*) de los sistemas multiprocesador heterogéneos, soportando en principio todo tipo de configuraciones. A pesar de las indudables ventajas que comportan estas APIs estándar, la realidad es que los resultados que se obtienen dependen fuertemente de la calidad de la implementación que exista para cada plataforma *hardware* y a veces distan de ser óptimos, muy especialmente en sistemas empotrados. En estos últimos, además, es frecuente que el soporte al paralelismo a nivel de tarea, incorporado en revisiones relativamente recientes de ambos estándares, sea deficiente o directamente inexistente [19, 20].

## 1.1.4 GNU Radio: una herramienta de código abierto para radio software

Todo lo expuesto hasta ahora indicaba en el momento de iniciar este trabajo de tesis que existía un problema sin resolver en el ámbito de la programación de sistemas multiprocesador heterogéneos para aplicaciones de radio *software*, especialmente en sistemas empotrados, y por ello se decidió enfocar la investigación en este problema.

Al comenzar el trabajo parecía razonable, antes de comenzar de cero, buscar alguna herramienta o metodología de programación que pudiera emplearse como punto de partida. El abanico de posibilidades no era muy grande, ya que la mayoría de las herramientas existentes presentaban problemas de acceso (bien por ser desarrollos comerciales o simplemente por no estar fácilmente disponibles) o parecían requerir un esfuerzo considerable antes de empezar a obtener resultados.

La solución se encontró en un *kit* de desarrollo para aplicaciones de radio *software* llamado *GNU Radio* [21]. Como su nombre indica, este *software* se distribuye bajo la Licencia Pública General de GNU (*GNU General Public License*) [22], y es por tanto *software* libre y de código abierto, por lo que es plenamente accesible para su estudio y modificación. Al estar orientado precisamente a aplicaciones de radio *software* emplea un modelo de programación basado en flujo de datos que aprovecha de forma natural el paralelismo a nivel de tarea inherente a estos sistemas, y aunque en principio está pensado para el uso en ordenadores típicos de escritorio sus características hacían pensar que podía emplearse sin grandes dificultades en sistemas empotrados.

Por tanto, se decidió emplear este *software* como base de este trabajo de tesis, desarrollando sobre el mismo una metodología de programación de sistemas multiprocesador heterogéneos.

## 1.2 OBJETIVOS Y METODOLOGÍA

El objetivo principal de este trabajo de tesis es:

Elaborar una metodología de desarrollo para aplicaciones de radio software sobre plataformas multiprocesador heterogéneas aplicable a sistemas empotrados.

La metodología empleada en el trabajo de tesis ha sido la siguiente:

- Se ha seleccionado una aplicación de referencia lo suficientemente compleja para permitir evaluar los resultados obtenidos. La aplicación seleccionada ha sido un receptor de televisión digital terrestre DVB-T.

- Se ha empleado una herramienta comercial (Matlab/Simulink) para crear un modelo funcional del receptor DVB—T. Se ha utilizado después este modelo para implementar el receptor en una plataforma específica para radio *software* basada en la combinación de un DSP y una FPGA. La implementación ha servido para evaluar las posibilidades que ofrecen varias herramientas de diseño de alto nivel basadas en Simulink.

- En paralelo se ha realizado una segunda implementación en PC utilizando GNU Radio. Esta implementación ha servido para conocer en profundidad las posibilidades de esta herramienta de *software* libre y llegar a la conclusión de que es posible utilizarla como base para elaborar una metodología de desarrollo de sistemas de radio *software* sobre arquitecturas multiprocesador heterogéneas.

- A continuación se ha diseñado un mecanismo que permite extender GNU Radio para su uso en este tipo de arquitecturas y validar el diseño con una implementación en una arquitectura completa. Para esta implementación se ha seleccionado una tarjeta de desarrollo basada en el procesador OMAP 3530 de Texas Instruments, que combina un procesador de propósito general y un DSP.

- Por último se ha repetido el trabajo de adaptación para la familia de procesadores KeyStone II del mismo fabricante y se ha portado el receptor DVB-T a una plataforma de desarrollo basado en un procesador de esta familia. Esto ha permitido generalizar la metodología empleada en el trabajo y validar el resultado obtenido con ella.

La figura 3 resume de forma gráfica los pasos que se han descrito.

Figura 3: Metodología empleada en el trabajo de tesis

## 1.3 ORGANIZACIÓN DE LA MEMORIA

La memoria se ha estructurado en siete capítulos. El primer capítulo es esta introducción en la que se justifica la motivación de este trabajo de tesis y se describen sus objetivos y la metodología empleada.

En el capítulo 2 se proporciona información relevante sobre el contexto en el que se ha desarrollado el trabajo de tesis: se describe el estándar de televisión digital terrestre DVB–T, empleado como aplicación de referencia para la evaluación de los resultados obtenidos; se amplía información sobre el concepto de radio *software*, sus

características y sus aplicaciones; y se describe el estado del arte en cuanto a arquitecturas *hardware* para aplicaciones de radio *software* y metodologías de programación empleadas en estas arquitecturas.

En el capítulo 3 se describe el trabajo de modelado e implementación del receptor DVB–T con Matlab/Simulink, se evalúan los resultados obtenidos con las herramientas automáticas de implementación y se describe la implementación del receptor DVB–T con GNU Radio.

En el capítulo 4 se describe el funcionamiento interno de GNU Radio y su extensión para adaptarlo a sistemas multiprocesador heterogéneos que emplean diversos procesadores como aceleradores para algunas funciones. La extensión se describe de forma genérica, de modo que sea válida para cualquier plataforma.

En el capítulo 5 se describe cómo se ha implementado la extensión propuesta en dos plataformas basadas, respectivamente, en procesadores OMAP 3530, que incluye un núcleo de propósito general ARM Cortex A8 y un núcleo DSP C64x+, y KeyStone II, que incluye cuatro núcleos de propósito general ARM Cortex A17 y ocho núcleos DSP C66. La implementación en OMAP 3530 sirve como prueba de concepto para validar el mecanismo de extensión propuesto. La implementación en KeyStone II incluye, además de la extensión de GNU Radio, el receptor DVB–T y su modificación para que haga uso de los núcleos DSP.

En el capítulo 6 se resume la metodología de programación de sistemas multiprocesador heterogéneos que se propone como resultado principal de este trabajo de tesis, incluyendo las directrices para poder aplicarla a otras plataformas de desarrollo.

Finalmente, en el capítulo 7 se resumen las aportaciones realizadas en la tesis, incluyendo las publicaciones y comunicaciones a congresos que se han llevado a cabo durante su desarrollo, y se proponen algunas ideas de continuación de la línea de trabajo de la tesis.

La memoria concluye con la relación de referencias bibliográficas que se han consultado durante el desarrollo de la tesis.

#### 2.1 INTRODUCCIÓN

En este capítulo se describen brevemente las tecnologías y la aplicación que han sido utilizadas en el desarrollo de esta tesis y que permiten contextualizar la investigación llevada a cabo. A la vez que se realiza una descripción de las mismas, con objeto de que la memoria de tesis resulte autocontenida, se establece también cuál es el estado del arte.

En el apartado 2.2 se describe el estándar de televisión digital terrestre DVB-T, cuyo receptor ha sido utilizado en esta tesis como aplicación de referencia para validar la metodología de diseño sobre arquitecturas multiprocesador heterogéneas. Se ha elegido esta aplicación por su elevada complejidad y por la experiencia previa del grupo de investigación en el que se ha desarrollado la tesis en los sistemas de codificación/decodificación de televisión digital. Sin embargo, con el trabajo de esta tesis se ha pretendido avanzar más en la integración del sistema incluyendo, en lo posible, el receptor de radio.

Para la integración del receptor de radio, resulta interesante aplicar el concepto de *radio software* ya presentado en el capítulo anterior y que se describe con más detalle en el apartado 2.3. La materialización de sistemas de radiocomunicación sobre procesadores programables, empleando técnicas de tratamiento digital de la señal, se viene utilizando desde hace ya algunos años, si bien, el uso de arquitecturas multiprocesador heterogéneas como tecnología de soporte para estas implementaciones no es tan frecuente y, además, su diseño plantea unos retos metodológicos no triviales, a los que esta tesis aporta contribuciones.

En el apartado 2.4 se describen diversas arquitecturas comerciales o propuestas en la literatura científica, que pueden servir como soporte de las aplicaciones de *radio software*. Se describen arquitecturas convencionales, procesadores especializados, procesadores reconfigurables y los entornos de desarrollo asociados. Finalmente se describen arquitecturas multiprocesador heterogéneas en las que la coexistencia de uno o varios núcleos de procesadores de propósito general y uno o varios núcleos de procesadores digitales de señal, se perfilan como la alternativa más flexible para este tipo de aplicaciones en las que los estándares evolucionan de forma muy rápida. Sin

embargo, este tipo de arquitecturas presentan el inconveniente, ya mencionado en el párrafo anterior, del coste del desarrollo sobre las mismas.

El capítulo concluye con el apartado 2.5, en el que se presentan algunas metodologías de diseño sobre arquitecturas multiprocesador heterogéneas, área en la que este trabajo de tesis realiza contribuciones.

#### 2.2 EL ESTÁNDAR DE TELEVISIÓN DIGITAL TERRESTRE DVB-T

En el inicio de este trabajo se decidió elegir un estándar de comunicaciones inalámbricas concreto para poder comparar los resultados que se fueran obteniendo en un marco común. Se decidió emplear DVB–T y su extensión para recepción en movilidad DVB–H como aplicación de referencia.

Desde entonces DVB–H, como se verá más adelante, ha perdido buena parte del interés que despertó inicialmente, y DVB–T está en proceso de ser sustituido por su sucesor DVB–T2. No obstante, la elección realizada sigue siendo válida para el fin que se perseguía, por lo que todo el trabajo realizado se ha mantenido orientado al estándar DVB–T. A fin de facilitar la descripción de las diversas implementaciones que se han ido realizando, a continuación se presenta una introducción a las características más relevantes de dicho estándar.

### 2.2.1 Introducción a la familia de estándares DVB

DVB (*Digital Video Broadcasting*) es una familia de estándares de origen europeo para televisión digital mantenidos por el Proyecto DVB [23], un consorcio formado por más de 180 empresas y organismos públicos, y publicados por ETSI (*European Telecommunications Standards Institute*).

La familia de estándares DVB está compuesta por más de cien normas, pero sin duda las que pueden considerarse principales son las que definen la transmisión de televisión digital por satélite (DVB–S), por cable (DVB–C) y terrestre (DVB–T). Los estándares DVB–S y DVB–C fueron publicados en 1994, seguidos tres años más tarde por DVB–T en 1997. Desde entonces DVB–T ha sido desplegado en más de 70 países en todo el mundo. En España, por ejemplo, las primeras licencias de emisión con este sistema se otorgaron en 1999 y en 2002 comenzó la emisión regular en *simulcast* (es decir, retransmitiendo el mismo contenido) de las cadenas de TV analógica con cobertura nacional.

Simultáneamente al desarrollo de DVB, la "Grand Alliance" estadounidense (un consorcio similar al Proyecto DVB) desarrolló el sistema ATSC (*Advanced Television Systems Committee*), y Japón hizo lo propio con el sistema ISDB (*Integrated Services*

Digital Broadcasting). Estos tres sistemas (DVB, ATSC e ISDB) son los empleados en prácticamente todo el mundo para la transmisión de televisión digital. Todos ellos utilizan MPEG–2 como sistema de codificación de fuente para audio y vídeo [24] y como trama de sistema [25]. Algunos años más tarde China desarrolló su propio sistema, llamado DTMB (Digital Terrestrial Multimedia Broadcast).

Durante la década de los 2000 el constante incremento de las capacidades de los terminales de telefonía móvil hizo pensar en la difusión de servicios audiovisuales a este tipo de dispositivos. Las redes de telefonía móvil 3G que comenzaban a desplegarse en esa época eran poco adecuadas para este tipo de servicios, lo que propició la aparición de nuevos sistemas de transmisión. Dentro de la familia DVB se publicaron los estándares DVB–H en 2004, orientado a la difusión terrestre, y DVB–SH en 2007, para la difusión vía satélite.

El estándar DVB–H, que es fundamentalmente una extensión de DVB–T para mejorar la recepción en condiciones de movilidad y disminuir el consumo de energía en el receptor, fue empleado en varias pruebas de campo, especialmente durante el campeonato mundial de fútbol que se celebró en Alemania en 2006. En ese mismo año varios operadores comenzaron a comercializar servicios basados en dicho sistema, tanto en Europa como en otros países. Sin embargo, al menos en Europa, el sistema ha sido un fracaso comercial y la mayoría de los operadores han cancelado sus servicios entre los años 2010 y 2012. Esto, unido a la evolución que entre tanto han experimentado los sistemas de telefonía móvil, con 4G completamente implantada y servicios 5G ya disponibles en grandes ciudades, hace muy improbable que el estándar DVB–H vuelva a tener alguna oportunidad de adopción significativa.

Mientras tanto el estándar DVB–T ya estaba plenamente establecido tanto en Europa como en múltiples países de todo el mundo. Entre los años 2006 y 2012 fueron cesando las emisiones de televisión analógica en toda Europa, un proceso que se conoció como el "apagón analógico" y que en España se produjo en abril de 2010.

Más o menos en ese período comenzaron también las emisiones comerciales de televisión en alta definición. En 2004 comienza a operar el canal HD1, emitido a través de los satélites Astra usando DVB–S. En 2008 comienza la emisión regular de TV en alta definición terrestre, usando DVB–T, en Italia y Francia.

Las emisiones en alta definición multiplican por cuatro o cinco la tasa binaria requerida por cada servicio. Este impacto fue mitigado en parte cambiando el estándar de compresión de vídeo de MPEG–2 a MPEG–4 o MPEG–4/AVC en las emisiones en HD, pero simultáneamente se trabajó en la evolución del estándar DVB–T para aumentar la capacidad de cada canal. En 2009 se publicó el estándar DVB–T2, y en ese mismo año comenzaron las emisiones en alta definición en Reino Unido empleando este nuevo estándar. Actualmente más de 30 países han comenzado el despliegue de

Figura 4: Mapa de adopción de estándares de televisión digital terrestre [26]

servicios de televisión digital terrestre basados en DVB-T2, y otros 40 lo han adoptado. En total, 150 países en todo el mundo han desplegado o adoptado DVB-T o T2 como sistema de televisión digital terrestre (figura 4).

### 2.2.2 *Características de DVB*–T

Muchas de las características de DVB–T están heredadas de los estándares que le precedieron, DVB–S y DVB–C. Algunos de los requisitos más significativos que se definieron para el sistema previamente a su diseño fueron los siguientes [27]:

- El sistema debía ser tan similar como sea posible a los sistemas de transmisión via satélite y cable.

- El sistema debía proporcionar un área de cobertura óptima en recepción estacionaria con una antena de tejado. Era deseable la recepción estacionaria con receptores portables, pero la recepción móvil no era un objetivo de diseño.

- Debía ser posible la transmisión en redes terrenas de frecuencia única (SFN, Single Frequency Network).

- El estándar debía asegurar que con la tecnología disponible en el año 1997 fuera posible producir un receptor doméstico con un precio razonable.

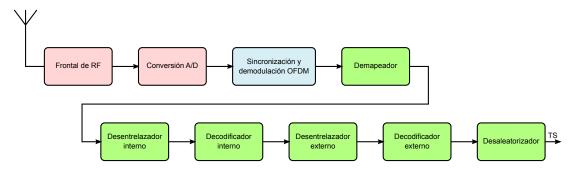

Figura 5: Diagrama de bloques funcional de un transmisor DVB-T [28]

■ El sistema debía ofrecer la posibilidad de emplear transmisión jerárquica.

Las características técnicas de DVB–T están determinadas en gran medida por estos requisitos. Por ejemplo, el requisito de posibilitar las SFN determinó el uso de OFDM (*Orthogonal Frequency Division Multiplex*) como técnica de modulación, y el esquema de protección contra errores mediante códigos encadenados que se describirá más adelante es el mismo que se diseñó para DVB–S.

La figura 5 muestra un esquema funcional de un transmisor DVB–T. La entrada es un flujo de transporte (*Transport Stream*, TS) MPEG–2 que contiene todos los servicios que se desean transmitir, o dos TS si se emplea transmisión jerárquica. Esta técnica permite contrarrestar la brusca degradación de la calidad de recepción al disminuir la calidad de la señal recibida que caracteriza a los sistemas de transmisión digital, frente a la degradación gradual que experimentan los sistemas analógicos en condiciones similares.

La transmisión jerárquica permite transmitir simultáneamente dos canales, uno de alta prioridad que puede decodificarse aunque la señal recibida sea débil a costa de una capacidad relativamente reducida, y otro de baja prioridad con mayor capacidad pero que precisa de una mejor calidad de recepción. Por cada canal se transmite un TS distinto que puede contener, por ejemplo, dos versiones con distinta calidad del

mismo programa. La vía de procesado del canal de baja prioridad aparece punteada en la figura 5.

A continuación se ofrece una breve descripción de cada paso del procesado que efectúa el transmisor antes de emitir la señal de radio.

## 2.2.2.1 Adaptación del múltiplex y dispersión de energía

El TS está compuesto por paquetes de longitud fija (188 bytes) que comienzan con un byte de sincronización fijo,  $47_{HEX}$ . Este módulo genera una secuencia pseudoaleatoria de bits que se combinan mediante una operación lógica XOR con los bits del TS, de modo que se aleatoriza la secuencia de entrada evitando la aparición de patrones repetitivos. Estos patrones tendrían más adelante el efecto de que la energía de la señal transmitida no se distribuyera de manera uniforme por el canal de transmisión, lo que podría tener consecuencias indeseadas [27, p. 191] que no corresponde detallar aquí.

Los paquetes de transporte se agrupan de ocho en ocho. Los bytes de sincronización de cada paquete se dejan inalterados (no se combinan con la secuencia pseudo-aleatoria) y el primer byte de cada grupo de ocho se invierte bit a bit, lo que permite recuperar en el receptor la sincronización a nivel de TS.

## 2.2.2.2 Codificación

El flujo de transporte aleatorizado se protege frente a errores en la transmisión mediante la aplicación de dos códigos encadenados separados por una operación de entrelazado a nivel de byte. Esta forma de combinar dos códigos mejora enormemente la capacidad de corrección frente a la que se obtendría aplicando cualquiera de ellos por separado [29]. El entrelazado aumenta además la resistencia del código frente a errores producidos en ráfaga.

2.2.2.1CODIFICACIÓN EXTERNA Cada paquete de transporte se codifica mediante un código Reed Solomon acortado RS(204,188,8)¹ derivado del código RS(255,239, 8). Este código añade 16 bytes a cada paquete de transporte, que pasa así de 188 a 204 bytes.

Esta codificación permite corregir cualquier error que afecte a un máximo de 8 bytes cualesquiera de un paquete de transporte.

<sup>1</sup> Un código RS(n,k,t) toma como entrada palabras de k símbolos y genera palabras codificadas de n símbolos, y puede corregir errores en t símbolos en la palabra codificada [30]. Si el código opera sobre  $GF(2^8)$ , como es el caso, cada símbolo está compuesto por 8 bits (1 byte).

Figura 6: Entrelazado y desentrelazado externo en un transmisor DVB-T [28]

2.2.2.2.2ENTRELAZADO EXTERNO El flujo de paquetes de transporte codificados se introduce en un entrelazador convolucional de Forney [31] con I = 12 y M = 17: los bytes de entrada se van distribuyendo cíclicamente por doce ramas, cada una de las cuales tiene una FIFO con una longitud que va creciendo en múltiplos de diecisiete bytes. La figura 6 muestra tanto el proceso de entrelazado como el de desentrelazado.

Este proceso de entrelazado hace que los bytes que a la salida del entrelazador son contiguos pertenezcan en realidad a doce paquetes distintos o, visto de otro modo, hace que los 204 bytes de un paquete de transporte codificado se distribuyan a lo largo de 2244 bytes  $(I \times (I-1) \times M)$  a la salida del entrelazador. Esto aumenta notablemente la resistencia del código ante errores en ráfaga.

La estructura del entrelazador hace que a su salida se mantenga el patrón de sincronización de los paquetes de transporte: un byte de sincronización ( $47_{HEX}$ ) cada 204 bytes con uno de cada ocho bytes de sincronización invertido.

2.2.2.2.3CODIFICACIÓN INTERNA A la salida del entrelazador se aplica un código convolucional² de tasa 1/2 con 64 estados (K=7) cuyos polinomios generadores son  $G_1=171_{OCT}$  y  $G_2=133_{OCT}$  (figura 7).

A este código se le puede aplicar opcionalmente uno de entre cuatro patrones de punteado, lo que permite obtener códigos de tasa 1/2 (sin punteado), 2/3, 3/4, 5/6 y 7/8. Esto permite seleccionar el mejor compromiso para cada red concreta entre robustez y eficiencia del código.

<sup>2</sup> Un código convolucional es un código lineal en el que la matriz generadora tiene una estructura tal que la operación de codificación puede verse también como una operación de filtrado o convolución [30]. La secuencia codificada puede así obtenerse a partir de las salidas intercaladas de uno o más filtros digitales que reciben como entrada la secuencia a codificar.

Figura 7: Codificador convolucional de DVB-T [28]

### 2.2.2.3 Entrelazado interno

A la salida de la cadena de aleatorización y codificación que se acaba de describir se obtiene un flujo de bits, o dos si se emplea transmisión jerárquica ya que en este caso cada uno de los canales tiene su propia cadena de aleatorización y codificación (véase la figura 5). El entrelazado interno combina estos dos flujos de bits (si se da el caso) en uno solo y los reordena de modo que se maximice la probabilidad de que un posible error de demodulación en una portadora OFDM individual se traduzca en un error en un único bit [27, p. 247].

La salida del entrelazador interno está compuesta por grupos de dos, cuatro o seis bits, en función de la modulación que se escoja para las portadoras de datos individuales. Existen por tanto cinco configuraciones distintas del entrelazador interno: modulación no jerárquica modulando las portadoras individuales con QPSK, 16QAM o 64QAM, y transmisión jerárquica modulando las portadoras individuales con 16QAM o 64QAM.

### 2.2.2.4 Mapeado de símbolos